7 纳米芯片是当今已量产之最先进制程产品,金属材料加入钴(Co)是关键,但钴(Co)真的完全取代原先的铜(Cu)了吗?

人工智慧及大数据时代来临,芯片也必须透过不断微缩提升效能?然而面对7 纳米先进制程,如何生产出效能更高、耗电更少、面积更小,又符合可靠度要求的芯片,是当今半导体制程上的重要课题。

当今,随着摩尔定律,半导体7 纳米先进制程已进入量产阶段,从材料工程上来看,电晶体接点与导线的重大金属材料进行变革,是解除7 纳米以下先进制程效能瓶颈的关键。

这重大的金属材料就是──钴(Co)。然而坊间传言以钴(Co)取代铜(Cu)的真实性如何?

宜特材料分析实验室这次直接实测已量产的7 纳米芯片,带您进入7 纳米的微缩世界。

▲ 图1

降低RC Delay,提升芯片运行速度

在积体电路中,「电阻─电容延迟时间」(RC Delay)是影响半导体元件的速度或性能的重要参数之一。

随着半导体制程推进至7 纳米,不仅金属连线(interconnect)层数越趋增加,导线间的距离也不断微缩;当电子讯号在层数非常多的金属连线(interconnect)间传送时,其产生的「电阻─电容延迟时间」(RC Delay),将严重减低半导体元件的速度。如何降低「电阻─电容延迟时间」(RC Delay)、增加半导体元件运行速度,是一重要课题。

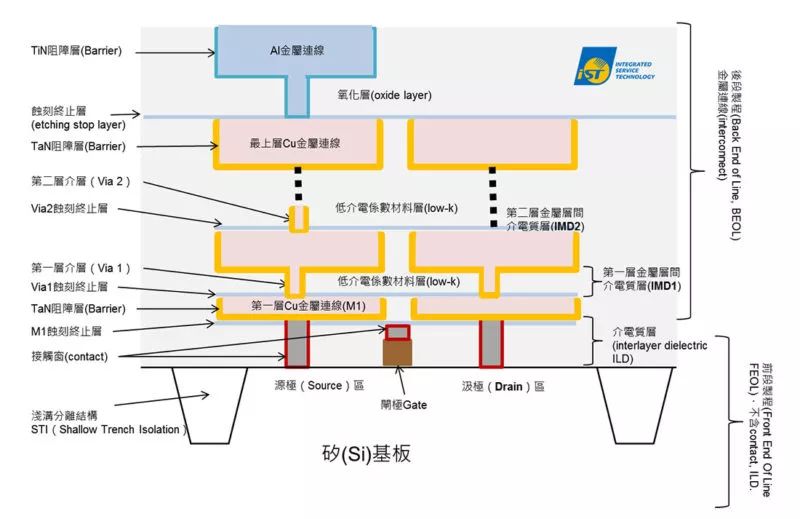

IC 制程微缩,阻障层有相对增加电阻的风险

铜(Cu)和铝(Al)是半导体后段制程(Back End Of Line,BEOL)金属连线(Interconnect)最常使用的金属材料。而铜主要会被用于先进制程的「金属连线」,来自于铜导电性比铝好,不过铜(Cu)原子在介电层的扩散系数远比铝原子大,为防止铜(Cu)扩散在介电层所造成线路短路。所以,在半导体制程,就必须使用更致密的「氮化钽」(TaN),取代柱状晶结构的「氮化钛」(TiN),借此避免铜扩散。

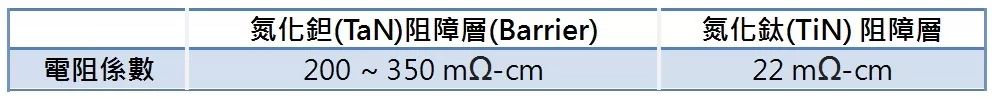

然而,此氮化钽(TaN)比氮化钛(TiN)的电阻系数大很多,相差十倍以上(参见表1),使用氮化钽(TaN)为铜的阻障层,将会有使金属连线电阻增加的风险。

▲ 表1:TaN 及TiN 电阻系数。

金属线上的电阻为「铜线电阻」加「氮化钽(TaN)层电阻」的总和。铜线尺寸大时,氮化钽(TaN)层引起的电阻增加比例不大,可忽略不计。但是当芯片微缩到非常小,促使铜线的尺寸也逐渐缩小时,氮化钽(TaN)层贡献的电阻比例就愈来愈大。宜特材料分析实验室使用并联电阻简化计算氮化钽层电阻贡献度(见表2)。铜线横截面尺寸由200 纳米降到20 纳米,则氮化钽层电阻贡献度约增加大于40 倍。

▲ 表2:氮化钽层电阻贡献度,利用并联电阻简化计算。

然而,在铜(Cu)制程中,因铜的容易扩散的特性关系,所以也不能藉由降低氮化钽(TaN)层的「厚度」来减少电阻,否则就会失去阻障功能。因此在7 纳米IC 制程中,使用新材料取代铜导线或阻障层变成很重要的课题。

降低7 纳米芯片的电阻,金属材料是选用是关键那该如何减低氮化钽(TaN)层的电阻呢?调整该层的金属材料就成为关键。经研究,发现金属钴(Co)是加入氮化钽(TaN)阻障层的极佳候选材料,钴(Co)不但降低阻障层的电阻,而且可以降低阻障层厚度,一举两得。

双层接触窗设计,让钴(Co)发挥最大效能金属导线和矽基板上半导体元件之间的连结称为接触窗(contact),主要是靠钨(W)连结,其阻障层材料是氮化钛(TiN)。在铜金属化制程中,如何降低W / TiN 的接触窗的电阻,钴(Co)又成为最佳候选者。但是,用钴(Co)直接完全取代W / TiN 直接和铜接触,则铜和钴容易固溶在一起,造成金属导线电迁移性能会变差。于是有了双层接触窗的制程设计。

实测7 纳米制程芯片,透视钴(Co)是否完全取代铜(Cu)剖析完为什么要使用钴(Co)的原因后,宜特材料分析实验室进行实测,一起来看看钴(Co)是用在7 纳米制程芯片的那些地方?钴(Co)真的完全取代铜(Cu)了吗?

前期样品制备作业为了执行分析7 纳米先进制程产品的分析,宜特材料分析实验室采购市售手机相关部品,取得Kirin 980 CPU。由于此CPU 是封装在手机电路板上,必须先进行相关部品的拆解(Tear down),以及相关结构观察的分析工程,包括X 光分析、去锡球、去封装、去胶、红外线定位、研磨、吃酸、CPU / DRAM 双芯片分离等技术,最后终于取得Kirin 980 芯片。

利用TEM 实际观察宜特材料分析实验室利用穿透式电子显微镜(Transmission electron microscope,TEM),搭配高性能的能量散布X 射线谱术(Energy-dispersive X-ray spectroscopy,EDS / EDX),借此解析7 纳米芯片的前段制程(Front End Of Line,FEOL)及后段制程(Back End Of Line,BEOL)。

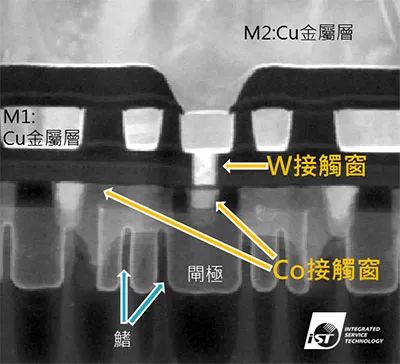

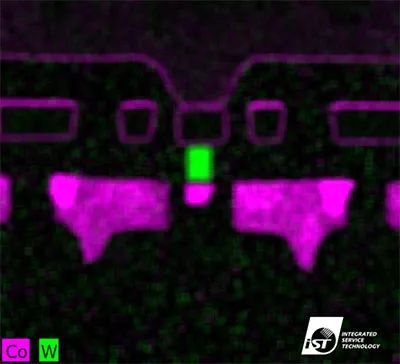

宜特材料分析实验室透过TEM 及EDS 观察芯片结构里头第一层(M1)与第二层(M2)金属层,解析7 纳米的鳍状电晶体(FinFET)、闸极(Gate)、接触窗(Contact)(见图2),与相对应钴(Co)及钨(W)(见图3)的成分分布。

▲ 图2:STEM HAADF 影像,显示鳍状电晶体、闸极、接触窗、M1 和M2 等结构。

▲图3:桃红色为钴(Co)成分,草绿色为钨(W)成分,对照图2,即可了解钴和钨在结构里分布的情形。

由图2 及图3 两张图比较,宜特材料分析实验室观察到钴(Co)成为「接触窗」及「阻障层」材料,而且钴(Co)包覆了整个第一层(M1 )铜金属层的结构,成为阻障层材料。但Co 没有完全取代接触窗的W / TiN,可能是因为接触窗制程与阻障层制程使用不同类型制程,造成Co 与周围材料反应的状况不同,致使接触窗的Co 无法完全取代W/TiN。

结论由TEM 结果可知,钴(Co)的用途并非取代铜(Cu)。钴用在铜的阻障层,且只有取代一半的接触窗。因此宜特材料分析实验室得以证明钴(Co)在7 纳米先进制程产品,并未完全取代铜(Cu)。

免责声明:本网站所转载的文字、图片与视频资料版权归原创作者所有,如果涉及侵权,请第一时间联系本网删除。

官方微信

《中国腐蚀与防护网电子期刊》征订启事

- 投稿联系:编辑部

- 电话:010-62313558-806

- 邮箱:fsfhzy666@163.com

- 中国腐蚀与防护网官方QQ群:140808414